Tìm hiểu IC 74HC595

74HC595 là gì

74HC595 là một thanh ghi dịch (shift register) hoạt động trên giao thức nối tiếp vào song song ra (Serial IN Parallel OUT).

Nó nhận dữ liệu nối tiếp từ vi điều khiển và sau đó gửi dữ liệu này qua các chân song song.

Có thể tăng 8 chân đầu ra bằng cách sử dụng chip đơn.

Cũng có thể kết nối song song nhiều hơn 1 thanh ghi dịch.

Giả sử đã kết nối ba thanh ghi dịch với bộ vi điều khiển, các chân đầu ra được tăng lên 8 x 3 = 24.

>>> Tham khảo giá và datasheet các sản phẩm

https://dientutuonglai.com/san-pham/?keyword=74hc595

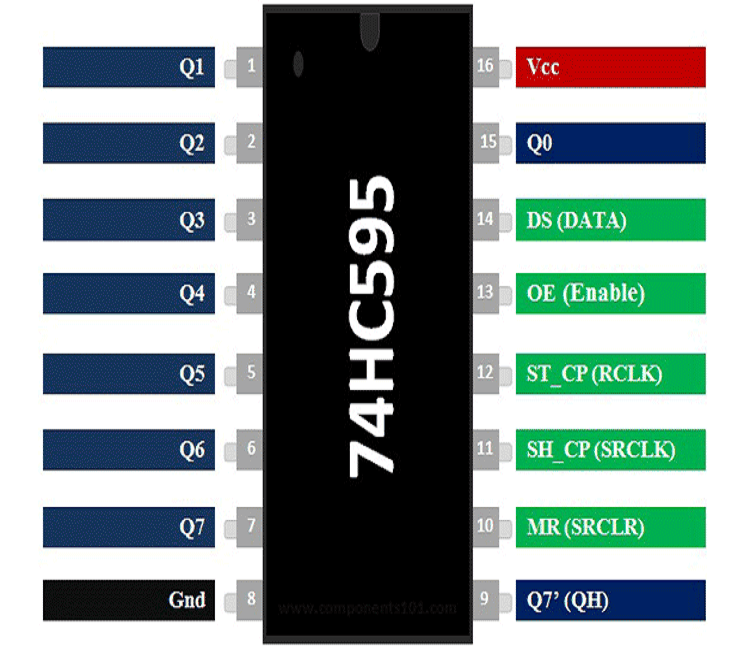

Sơ đồ chân 74HC595

|

Số chân |

Tên chân |

Mô tả |

|

1, 2, 3, 4, 5, 6, 7 |

Chân output (Q1 đến Q7) |

74hc595 có 8 chân đầu ra, trong đó có 7 chân này. Chúng có thể được kiểm soát nối tiếp |

|

8 |

Ground |

Nối đất |

|

9 |

(Q7’) Serial Output |

Chân này được sử dụng để kết nối nhiều hơn một 74hc595 dưới dạng xếp tầng |

|

10 |

(MR) Master Reset |

Reset tất cả các đầu ra ở mức thấp. Phải giữ ở mức cao để hoạt động bình thường |

|

11 |

(SH_CP) Clock |

Đây là chân đồng hồ mà tín hiệu đồng hồ phải được cung cấp từ vi điều khiển hoặc vi xử lý |

|

12 |

(ST_CP) Latch |

Chân Latch dùng để cập nhật dữ liệu vào các chân đầu ra. Nó kích hoạt mức cao |

|

13 |

(OE) Output Enable |

Chân OE được sử dụng để tắt đầu ra. Phải giữ ở mức thấp để hoạt động bình thường |

|

14 |

(DS) Serial Data |

Đây là chân mà dữ liệu được gửi đến, dựa trên đó 8 đầu ra được điều khiển |

|

15 |

(Q0) Output |

Chân đầu ra đầu tiên |

|

16 |

Vcc |

Chân này cấp nguồn cho IC, thường sử dụng + 5V |

Đặc tính thông số kỹ thuật 74HC595

8-bit, thanh ghi dịch nối tiếp vào song song ra

Điện áp hoạt động: 2V đến 6V

Mức tiêu thụ điện: 80uA

Source ra / dòng sink: 35mA

Điện áp đầu ra bằng điện áp hoạt động

Điện áp đầu vào mức cao tối thiểu: 3,15V @ (Vcc = 4,5V)

Điện áp đầu vào mức thấp tối đa: 1.35V @ (Vcc = 4.5V)

Có thể dễ dàng xếp tầng với nhiều IC hơn để có nhiều đầu ra hơn

Tần số đồng hồ tối đa: 25Mhz @ 4.5V

Có các gói PDIP, GDIP, PDSO 16 chân

Thanh ghi dịch thay thế

|

STT |

Tên |

Loại |

|

1 |

4035 |

Thanh ghi dịch song song vào song song ra 4 bit |

|

2 |

74LS379 |

Thanh ghi dịch song song tứ |

|

3 |

4014 |

Thanh ghi dịch tĩnh 4 bit |

|

4 |

74LS166 |

Thanh ghi dịch 8 bit |

|

5 |

74LS323 |

Thanh ghi dịch / lưu trữ 8 bit |

|

6 |

74LS164 |

Thanh ghi S/P |

|

7 |

4015 |

Thanh ghi tĩnh 4 bit kép |

|

8 |

74LS299 |

Thanh ghi dịch / lưu trữ 8 bit |

Nơi sử dụng IC 74HC595

74HC595 là một thanh ghi dịch nối tiếp vào song song ra 8 bit, tức là nó có thể nhận (đầu vào) dữ liệu nối tiếp và điều khiển 8 chân đầu ra song song. Điều này rất tiện dụng khi không có đủ chân GPIO trên vi điều khiển hoặc vi xử lý để kiểm soát số lượng đầu ra cần thiết. Nó thường được sử dụng trong các dự án mà số lượng tương đối lớn LED phải được điều khiển thông qua vi điều khiển. Nó cũng có thể được sử dụng để giao tiếp màn hình LCD vì có thể hoạt động như bit dữ liệu cho màn hình LCD. Nó cũng có thể được sử dụng để điều khiển tải 5V như relay thông qua vi điều khiển 3,3V vì điện áp mức cao chỉ là 3,15. Vì vậy, nếu bạn đang tìm một IC để giảm sử dụng các chân GPIO trên vi điều khiển thì IC này là sự lựa chọn phù hợp.

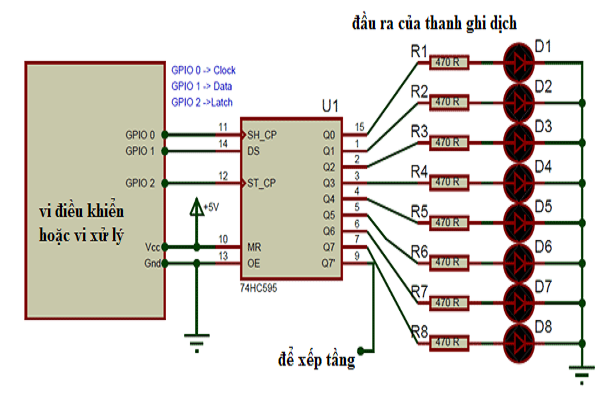

Cách sử dụng IC 74HC595

Thanh ghi dịch 74HC595 thường được sử dụng với bộ vi điều khiển hoặc bộ vi xử lý để mở rộng các chức năng của GIPO. Nó chỉ yêu cầu 3 chân kết nối với MCU, đó là Clock, Data và Latch. Nó có điện áp hoạt động rộng từ 2V đến 6V. Dưới đây là một mạch ứng dụng của IC:

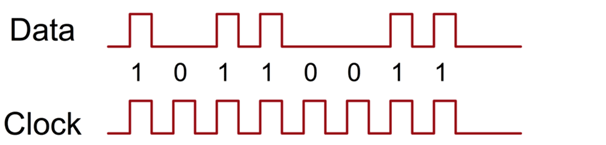

Các chân 11, 14 và 12 được kết nối với các chân GPIO của vi điều khiển. Trong đó chân 11 là Clock phát xung nhịp không đổi để giữ thời gian. Chân 14 là Data gửi dữ liệu về chân đầu ra nào phải ở mức thấp và chân nào sẽ ở mức cao. Chân 12 là Latch cập nhật dữ liệu nhận được vào các chân đầu ra khi đặt ở mức cao, chân này cũng có thể được giữ ở mức cao vĩnh viễn. Hình ảnh dưới đây sẽ giúp bạn hiểu rõ hơn.

Như bạn có thể thấy clock là dòng xung liên tục và dữ liệu chỉ tăng cao ở nơi tương ứng nơi đầu ra phải đạt mức cao. Ví dụ ở đây, giá trị nhị phân 0b10110011 được chuyển đến bộ vi điều khiển. Chân Master reset (MR) được sử dụng để reset các đầu ra, khi không sử dụng nó được giữ ở mức cao về vcc, tương tự như vậy, chân phải được giữ ở mức thấp khi không sử dụng.

Một ưu điểm quan trọng khác của vi mạch 74hc595 là nó có thể được xếp tầng để điều khiển hơn 8 đầu ra. Để thực hiện chúng ta sử dụng Q7 ’(chân 9), chân này được kết nối với chân data của IC 74HC595 thứ hai. Bằng cách này, 8 bit đầu tiên được gửi từ vi điều khiển sẽ được sử dụng bởi IC thứ nhất và 8 bit thứ hai sẽ được sử dụng bởi IC thứ hai.

Các ứng dụng

Mở rộng chân GPIO trên vi điều khiển hoặc vi xử lý

Dự án LED ma trận / khối lập phương

Giao diện LCD

Ứng dụng xếp tầng

Bộ điều khiển mức logic cao

>>> Tham khảo giá và datasheet các sản phẩm

- Linh Kiện Điện Tử, Linh Kiện Công Nghiệp – Giải Pháp Nhập Số Lượng Theo Yêu Cầu Tối Ưu Cho Doanh Nghiệp

- Tại sao chọn Vinafe làm đối tác cung cấp linh kiện điện tử?

- Dịch Vụ Cung Cấp Linh Kiện Công Nghiệp – Giải Pháp Toàn Diện Cho Doanh Nghiệp Sản Xuất

- Chuyên cung cấp linh kiện điện tử chính hãng – linh kiện sửa máy – thiếc hàn Vinafe

- Thiếc hàn chất lượng cao – Giao nhanh – Giá tốt cho kỹ sư và xưởng sản xuất nhỏ

- THIẾC HÀN CHẤT LƯỢNG CAO – CHUẨN CHO KỸ SƯ & XƯỞNG SẢN XUẤT NHỎ

- Sự khác nhau giữa thiếc hàn 63/37 và thiếc hàn 60/40 – Hiểu đúng để chọn chuẩn

- Nhiệt độ nóng chảy hoàn hảo của thiếc hàn – Yếu tố quyết định chất lượng mối hàn

- Thiếc hàn chất lượng cao – Giao nhanh – Giá tốt cho kỹ sư và xưởng sản xuất nhỏThiếc Hàn Là Gì? Tìm Hiểu Về Vật Liệu Quan Trọng Ngành Hàn

- 5 Mẹo Chọn Nhà Cung Cấp Linh Kiện Uy Tín – Tránh Mua Phải Hàng Giả

Hotline: 0979 466 469