CD4052 là gì

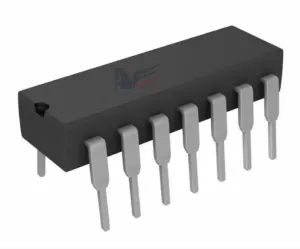

CD4052 là một IC 4 kênh kép có thể được sử dụng làm bộ ghép kênh 4: 1 và bộ phân kênh 1: 4. Nó là một vi mạch dựa trên logic CMOS thuộc dòng mạch tích hợp CD4000. Có thể sử dụng vi mạch này trong cả ứng dụng kỹ thuật số và analog. Nói cách khác, nó hoạt động cho cả mức điện áp analog và kỹ thuật số. Hơn nữa, nó có thể được điều khiển thông qua tín hiệu điều khiển kỹ thuật số và cung cấp điện trở rất thấp ở trạng thái BẬT. Nó có nhiều gói 16 chân bao gồm PDIP, CDIP, SOIC và TSSOP.

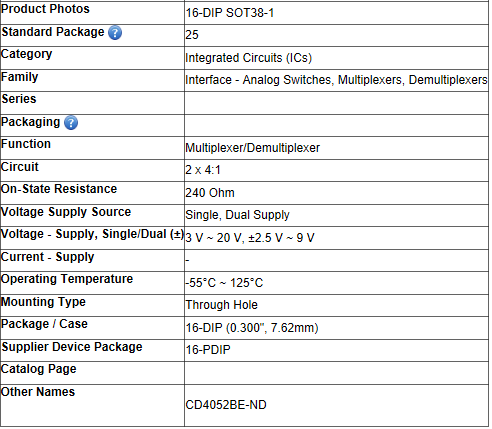

Tính năng thông số kỹ thuật của CD4052

Nó là một vi mạch 4 kênh có thể được sử dụng làm cả IC ghép kênh 4: 1 và IC phân kênh 1: 4

Nó hỗ trợ cả tín hiệu kỹ thuật số và tín hiệu analog. Dải điện áp của tín hiệu kỹ thuật số là 3 V đến 20 V và đối với mức tín hiệu analog ≤20 VP-P.

Nó có một tính năng ngắt trước khi thực hiện chuyển đổi giúp loại bỏ các kênh chồng chéo.

Chip có giải mã địa chỉ nhị phân.

Nó được kiểm tra 100% cho dòng điện tĩnh ở 20 V

Độ trễ lan truyền ở 5V là 400ns.

Ở 18V, dòng điện đầu vào tối đa là 1 µA trên phạm vi nhiệt độ của gói đầy đủ và đối với 25 ° C, nó là 100nA.

Điện áp hoạt động tối đa là 20V.

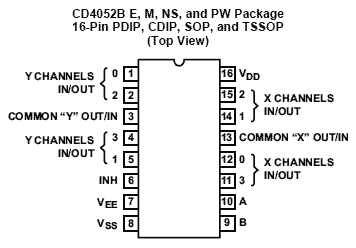

Sơ đồ chân CD4052

IC ghép kênh này gồm 16 chân. Hình ảnh bên dưới là sơ đồ chân của CD4052.

IC CD4052 có tổng cộng 16 chân. Tất cả các chân, tên của chúng và mô tả trong bảng dưới đây.

|

Số chân |

Tên chân |

Mô tả |

|

11, 12, 14, 15 |

X0, X1, X2, X3 |

Các chân đầu vào của kênh X |

|

1, 2, 4, 5 |

Y0, Y1, Y2, Y3 |

Các chân đầu vào của kênh Y |

|

3, 13 |

Y, X |

Đầu ra cho kênh X và Y |

|

6 |

INH (chân bật) |

Cho hoạt động bình thường, nên được nối ground |

|

7 |

Vss |

Nguồn âm |

|

8 |

Vdd |

ground của mạch |

|

9, 10 |

A, B |

Chân chọn cho kênh 0, 1, 2, 3 |

|

15 |

Nguồn dương |

Nơi sử dụng và cách sử dụng

CD4052 là IC ghép kênh / phân kênh vi sai 4 kênh kép có hai đầu vào điều khiển nhị phân A và B. Trong chế độ ghép kênh, nó lấy 4 đầu vào từ 4 kênh và trả về đầu ra trên kênh X, Y. và một đầu vào ức chế. Hai tín hiệu đầu vào nhị phân A và B có nhiệm vụ chọn kênh mà kênh nào nên được bật.

IC CD4052 cũng có thể hoạt động như một bộ phân kênh. Trong chế độ này, nó sẽ chỉ cần một đầu vào. Các chân A và B được chọn sẽ quyết định rằng đầu ra sẽ được gửi đến kênh 0, 1, 2 hoặc 3. Chân 15 được kết nối với nguồn điện và Vss được kết nối với ground của mạch. Khi chân ức chế chịu trách nhiệm cho phép và vô hiệu hóa các kênh. Khi nó được đặt logic 0, các kênh được bật. Các kênh bị vô hiệu hóa bất kể đầu vào nào được đặt trên các chân chọn khi chân ức chế được đặt với mức logic 1.

Ứng dụng CD4052

Nó có nhiều ứng dụng. Một số trong số đó là:

Ghép kênh và phân kênh analog và kỹ thuật số

Hệ thống truyền thông tin liên lạc để gửi nhiều tín hiệu cùng một lúc hoặc gửi một tín hiệu tại nhiều kênh sóng mang

Trong các mạch để chuyển đổi Analogue sang Digital và Digital sang Analogue để chuyển đổi

Gating tín hiệu

Các mạch chuyển mạch mạng chẳng hạn trong mạng điện thoại để gửi nhiều tín hiệu âm thanh trên một đường truyền.

Mạch logic có thể lập trình

Đơn vị logic số học (ALU) được kết nối với các thanh ghi bên trong bộ xử lý trung tâm (CPU). IC này có thể được sử dụng để chọn thanh ghi lưu dữ liệu hoặc đọc dữ liệu từ thanh ghi.

Bộ chuyển đổi nối tiếp sang song song

Datasheet

Xem datasheet của CD4052 tại ĐÂY