CD4028 là gì

CD4028 là bộ giải mã BCD sang thập phân hoặc nhị phân sang bát phân bao gồm 4 đầu vào và 10 bộ đệm đầu ra. Mã BCD được áp dụng cho 4 đầu vào, A, B, C và D, dẫn đến mức cao ở đầu ra được giải mã thập phân 1 của 10 đã chọn. Tương tự, mã nhị phân 3 bit áp dụng cho đầu vào A, B và C được giải mã thành hệ bát phân ở đầu ra 0-7. Tín hiệu mức cao ở đầu vào D ức chế giải mã bát phân và khiến đầu ra 0-7 ở mức thấp. IC có gói dòng kép (DIP) 16 giúp dễ dàng giao tiếp với các thiết bị TTL, CMOS và NMOS. IC cung cấp nhiều tính năng như khả năng chống nhiễu cao và tản nhiệt thấp.

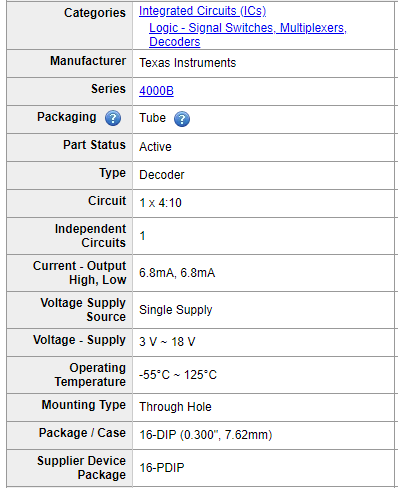

Đặc tính và thông số kỹ thuật CD4028

Dải điện áp nguồn rộng: 3.0V đến 15V

Khả năng chống nhiễu cao: 0,45 VDD (điển hình)

Khả năng tương thích TTL công suất thấp

Năng lượng thấp

"Logic dương" trên đầu vào và đầu ra

Sơ đồ chân CD4028

|

Số chân |

Tên chân |

Mô tả |

|

1 |

Q4 |

Đầu ra 4 của bộ giải mã |

|

2 |

Q2 |

Đầu ra 2 của bộ giải mã |

|

3 |

Q0 |

Đầu ra 0 của bộ giải mã |

|

4 |

Q7 |

Đầu ra 7 của bộ giải mã |

|

5 |

Q9 |

Đầu ra 9 của bộ giải mã |

|

6 |

Q5 |

Đầu ra 5 của bộ giải mã |

|

7 |

Q6 |

Đầu ra 6 của bộ giải mã |

|

8 |

VSS |

Nguồn source |

|

9 |

Q8 |

Đầu ra 8 của bộ giải mã |

|

10 |

A |

Địa chỉ đầu vào 0 |

|

11 |

D |

Địa chỉ đầu vào 1 |

|

12 |

C |

Địa chỉ đầu vào 2 |

|

13 |

B |

Địa chỉ đầu vào 3 |

|

14 |

Q1 |

Đầu ra 1 của bộ giải mã |

|

15 |

Q3 |

Đầu ra 8 của bộ giải mã |

|

16 |

VDD |

Nguồn drain |

Ứng dụng

Chuyển đổi mã

Giải mã địa chỉ

Bộ giải mã đèn báo

Datasheet

Xem datasheet của CD4028 tại ĐÂY