CD4027 là gì

CD4027 là IC gói JK Flip-Flop kép tốc độ cao dựa trên CMOS. Flip-Flop thường có thể hoạt động ở tốc độ 16MHz ngay cả ở điện áp cao như 15V với biên độ nhiễu thấp chỉ 2,5V.

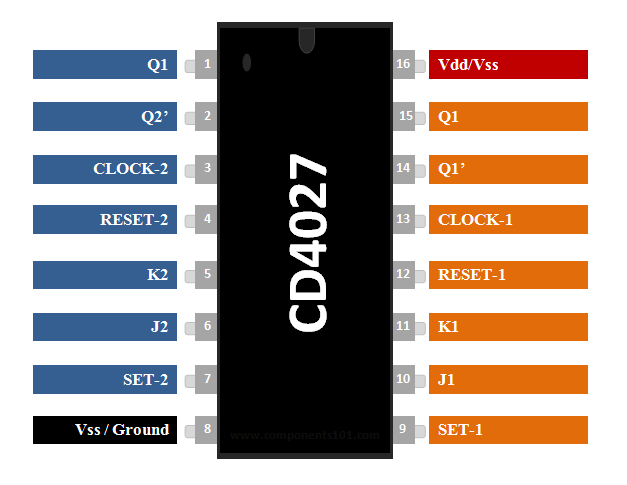

Sơ đồ chân CD4027

|

Số chân |

Tên chân |

Mô tả |

|

16 |

Vcc |

Cấp nguồn 5V cho IC |

|

8 |

Ground |

Nối mass của hệ thống |

|

JK Flip Flop 1 / JK Flip Flop 2 |

||

|

3, 13 |

Clock-1 / clock-2 |

Các chân này phải được cấp xung đồng hồ cho flip flop |

|

2, 7 |

Reset-1 / reset-2 |

Khi Preset cao, flip flop sẽ đặt Q = 1 chứ không phải Q = 0 |

|

4, 12 |

Clear-1 / clear-2 |

Khi Clear cao, flip flop sẽ đặt Q = 0 chứ không phải Q = 1 |

|

5, 11 |

K-1 / K-2 |

Chân đầu vào của flip flop |

|

6, 10 |

J-1 / J-2 |

Chân đầu vào khác của flip flop |

|

2, 14 |

Q-1(bar) / Q-2(bar) |

Chân đầu ra đảo ngược của flip flop |

|

1, 15 |

Q-1 / Q-2 |

Chân đầu ra của flip flop |

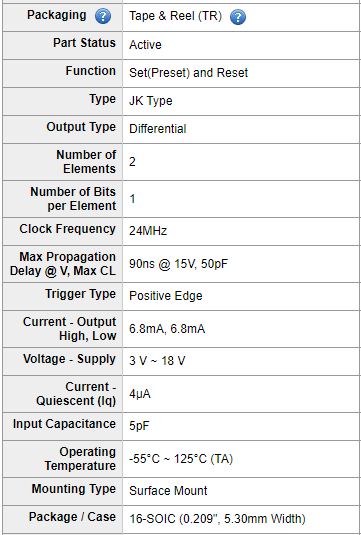

Tính năng thông số kỹ thuật của CD4027

IC gói JK Flip Flop kép

Tốc độ hoạt động: 16MHz

Điện áp hoạt động: 5V, 10V, 15V

Điện áp hoạt động tối đa: 20V

Thời gian tăng / giảm đầu vào ở 5V: 45us

Điện áp đầu vào mức cao tối thiểu: 2 V

Điện áp đầu vào mức thấp tối đa: 0,8 V

Có các gói PDIP, GDIP, PDSO 14 chân

Tương đương CD4027

74HC76

Lựa chọn thay thế JK Flip-Flop

74HC73a, 74LS107, 4027B

Nơi sử dụng CD4027 JK Flip-Flop

CD4027 là một IC flip flop JK kép trong dòng. Có nghĩa là nó có hai flip flop JK bên trong và mỗi flip flop có thể được sử dụng riêng lẻ dựa trên ứng dụng của chúng ta. Thuật ngữ flip flop JK được đặt theo tên người phát minh ra nó là Jack Kilby. JK Flip Flop được coi là flip flop hiệu quả nhất và có thể được sử dụng cho một số ứng dụng riêng. Flip-flop còn được gọi là thiết bị latch nghĩa là nó có thể nhớ một bit dữ liệu và latch đầu ra dựa trên nó, do thuộc tính này mà nó thường được sử dụng làm thanh ghi dịch chuyển, thanh ghi điều khiển, thanh ghi lưu trữ hoặc nơi có bộ nhớ nhỏ. Nhiều Flip Flop có thể được sử dụng nối tiếp để hoạt động như một EEPROM để chứa một lượng nhỏ dữ liệu. Flip flop JK được coi là phù hợp hơn cho ứng dụng thực tế vì bảng chân lý của nó là đầu ra của flip flop sẽ ổn định cho tất cả các loại đầu vào.

Vì vậy, nếu bạn đang tìm kiếm một IC cho mục đích latch hoặc hoạt động như một bộ nhớ lập trình nhỏ cho dự án thì IC này là sự lựa chọn phù hợp.

Cách sử dụng CD4027 Flip Flop

Như đã nói trước đó, chúng ta có hai flip flop JK trong IC này, IC được cấp nguồn + 5V thường là điện áp đầu vào và đầu ra tối thiểu và tối đa cho các chân đầu vào (J, K) và đầu ra (Q, Q bar) như trong các thông số kỹ thuật ở trên. Mạch bên dưới là kết nối mẫu điển hình cho flip-flop JK.

Các chân J và K là chân đầu vào cho Flip-Flop và chân Q và Q bar là chân đầu ra. Lưu ý rằng các chân đầu vào được kéo xuống đất thông qua một điện trở 1k hoặc nhỏ hơn, bằng cách này chúng ta có thể tránh được tình trạng chân cắm ở trạng thái nổi. Tức là chân sẽ được giữ tiếp đất khi không nhấn nút và khi nhấn nút, chân sẽ được giữ để cung cấp điện áp.

Nút reset phải được kéo lên thông qua một điện trở 1K và khi nối đất sẽ reset flip flop. Tín hiệu đồng hồ cho flip-flop JK chịu trách nhiệm thay đổi trạng thái của đầu ra. Flip-flop sẽ chỉ thay đổi đầu ra của nó trong tín hiệu đồng hồ của sườn lên. Tín hiệu đồng hồ ở đây chỉ là một nút nhấn nhưng có thể là dạng xung như tín hiệu PWM. Trạng thái đầu ra của flip flop có thể được xác định dưới dạng bảng chân lý bên dưới.

Thông thường trong quá trình hoạt động thường xuyên của IC, chân reset sẽ được đặt ở mức cao và xung đồng hồ có tần số đã biết sẽ được cung cấp cho chân đồng hồ, khi đó giá trị o J và K sẽ thay đổi dựa trên tín hiệu đầu vào và đầu ra tương ứng sẽ thu được trên các chân Q và Q bar. Vùng hoạt động này được đánh dấu bằng màu đỏ trên bảng chân lý ở trên.

Các ứng dụng

Thanh ghi dịch

Thanh ghi bộ nhớ / điều khiển

Mạch EEPROM

Thiết bị latch

Datasheet

Xem datasheet của CD4027 tại ĐÂY