74LS194 là gì

74LS194 là thanh ghi dịch chuyển hai chiều được thiết kế để kết hợp hầu như tất cả các tính năng mong muốn trong thanh ghi dịch chuyển. IC có các đầu vào song song, đầu ra song song, đầu vào nối tiếp dịch phải và dịch trái, đầu vào điều khiển chế độ vận hành và một đường xóa ghi đè trực tiếp (direct overriding clear).

Thanh ghi có bốn chế độ hoạt động riêng biệt, đó là: tải song song (mặt rộng), dịch sang phải (theo hướng QA về phía QD), dịch sang trái (theo hướng QD về phía QA), inhibit clock (không làm gì). Tải song song đồng bộ được thực hiện bằng cách áp dụng bốn bit dữ liệu và lấy cả hai đầu vào điều khiển chế độ, S0 và S1, CAO.

Dữ liệu được tải vào các flip-flop liên quan và xuất hiện ở các đầu ra sau quá trình chuyển đổi dương của đầu vào xung nhịp. Trong quá trình tải, luồng dữ liệu nối tiếp bị hạn chế. Chuyển sang phải được thực hiện đồng bộ với sườn lên của xung đồng hồ khi S0 ở mức CAO và S1 ở mức THẤP. Dữ liệu nối tiếp cho chế độ này được nhập ở đầu vào dữ liệu dịch chuyển bên phải. Khi S0 ở mức THẤP và S1 ở mức CAO, dữ liệu dịch chuyển sang trái một cách đồng bộ và dữ liệu mới được nhập vào đầu vào nối tiếp dịch chuyển sang trái. Quá trình xử lý flip-flop bị hạn chế khi cả hai đầu vào điều khiển chế độ đều THẤP.

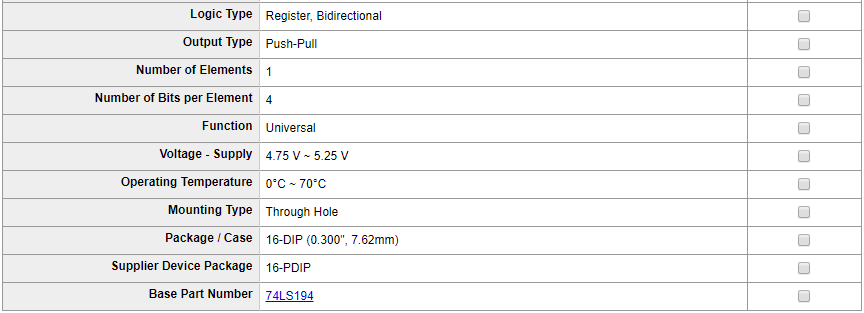

Đặc tính thông số kỹ thuật 74LS194

Đầu vào và đầu ra song song

Bốn chế độ hoạt động: tải song song đồng bộ, dịch phải, dịch trái, không làm gì

Đồng hồ kích hoạt sườn dương

Xóa ghi đè trực tiếp

Điện áp nguồn (VCC) 7 V

Điện áp đầu vào (VI) 7 V

Hoạt động trong phạm vi nhiệt độ 0 ° C đến + 70 ° C

Dải nhiệt độ bảo quản –65 ° C đến + 150 ° C

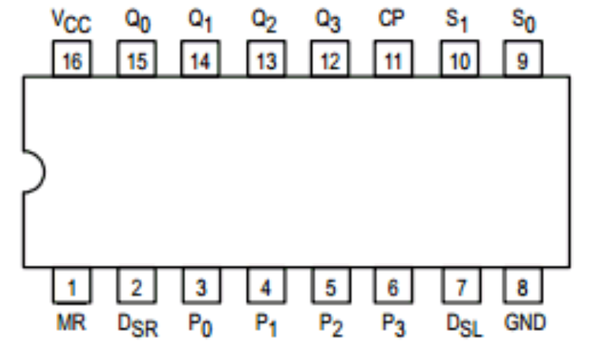

Sơ đồ chân 74LS194

Sơ đồ chân của IC 74LS194 như hình bên dưới. Ở đây S1 và S0 là đầu vào điều khiển chế độ (mode control), P0, P1, P2 và P3 là đầu vào dữ liệu song song (parallel data). DSL và DSR là đầu vào dữ liệu nối tiếp (serial data), CP là đầu vào đồng hồ (Active High Edge), Q0 đến Q3 là đầu ra dữ liệu song song và MR là viết tắt của Master Reset.

Datasheet

Tải datasheet của 74LS194 tại ĐÂY