74LS112 là gì

74LS112 là IC flip-flop JK kép có tính năng J, K, đồng hồ và bộ không đồng bộ riêng lẻ và đầu vào rõ ràng cho mỗi flip-flop. Nó chứa hai flip-flop J-K kích hoạt sườn âm độc lập với J-K riêng lẻ, đồng hồ và đầu vào rõ ràng trực tiếp. IC 74LS112 có điện áp làm việc đa dạng, nhiều điều kiện làm việc và giao tiếp trực tiếp với CMOS, NMOS và TTL. Đầu ra của IC luôn đi kèm với TTL, giúp dễ dàng làm việc với các thiết bị TTL và vi điều khiển khác.

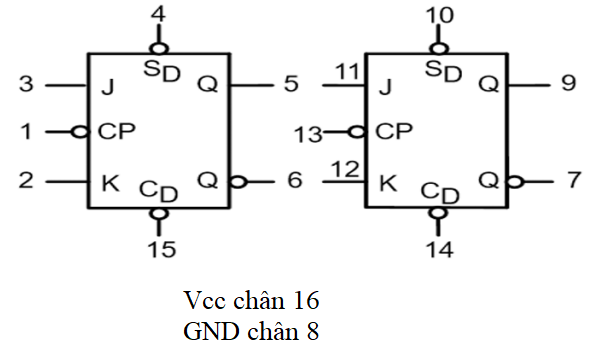

Sơ đồ chân 74LS112

|

Số chân |

Tên chân |

Mô tả |

|

1 |

1CLK |

Đầu vào đồng hồ 1 |

|

2 |

1K |

Chân đầu vào K1 |

|

3 |

1J |

Chân đầu vào J1 |

|

4 |

1PRE’ |

Chân active low preset 1 |

|

5 |

1Q |

Chân đầu ra Q1 |

|

6 |

1Q’ |

Chân đầu ra active low Q1 |

|

7 |

2Q’ |

Chân đầu ra active low Q2 |

|

8 |

GND |

Chân ground |

|

9 |

2Q |

Chân đầu ra Q2 |

|

10 |

2PRE’ |

Chân active low preset 2 |

|

11 |

2J |

Chân đầu vào J2 |

|

12 |

2K |

Chân đầu vào K2 |

|

13 |

2CLK |

Đầu vào đồng hồ 2 |

|

14 |

2CLR’ |

Chân active low / clear 2 |

|

15 |

1CLR’ |

Chân active low / clear 1 |

|

16 |

Vcc |

Nguồn chip |

Tính năng và thông số kỹ thuật 74LS112

Họ công nghệ: LS

IC gói JK Flip Flop kép

VCC (Tối thiểu): 4,75V

VCC (Tối đa): 5,25

Số bit (#): 2

Điện áp hoạt động (Nom): 5V

Tần số ở điện áp bình thường (Tối đa): 35MHz

Độ trễ lan truyền (Tối đa): 20ns

IOL (Tối đa): 8mA

IOH (Tối đa): - 0,4mA

Định mức: Catalog

Có các gói PDIP, GDIP, PDSO 16 chân

Các ứng dụng

PC và máy tính xách tay

Điện tử kỹ thuật số

Thanh ghi dịch

Datasheet

Xem datasheet của 74LS112 tại ĐÂY