TLV5620 là gì

TLV5620 là bộ chuyển đổi kỹ thuật số sang analog (DAC) đầu ra điện áp 8 bit tăng gấp bốn lần với đầu vào tham chiếu đệm (trở kháng cao). DAC tạo ra điện áp đầu ra nằm trong khoảng từ một hoặc hai lần điện áp tham chiếu và GND. Thiết bị này rất dễ sử dụng vì nó chạy từ một nguồn duy nhất từ 3 V đến 3,6 V. Chức năng thiết lập lại khi bật nguồn được tích hợp để đảm bảo các điều kiện khởi động lặp lại.

Điều khiển kỹ thuật số của TLV5620 qua một bus nối tiếp ba dây đơn giản, tương thích với CMOS và dễ dàng giao tiếp với tất cả các thiết bị vi xử lý và vi điều khiển phổ biến. Từ lệnh 11 bit bao gồm tám bit dữ liệu, hai bit chọn DAC và một bit phạm vi, bit sau cho phép lựa chọn phạm vi đầu ra lần 1 hoặc lần 2. Các thanh ghi DAC được lưu vào bộ đệm kép, cho phép ghi một tập hợp đầy đủ các giá trị mới vào thiết bị, sau đó tất cả các đầu ra của DAC cập nhật đồng thời thông qua điều khiển của LDAC. Các đầu vào kỹ thuật số có tính năng kích hoạt Schmitt để có khả năng chống ồn cao.

Gói phác thảo nhỏ (SO) 14 chân cho phép điều khiển kỹ thuật số các chức năng tương tự trong các ứng dụng quan trọng về không gian.

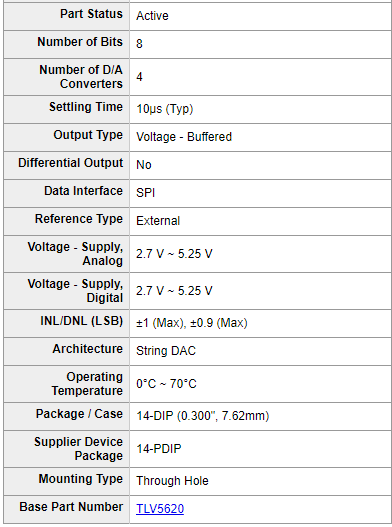

Đặc tính thông số kỹ thuật

Bốn DAC đầu ra điện áp 8 bit

Vận hành một nguồn 3-V

Giao diện nối tiếp

Đầu vào tham chiếu trở kháng cao

Có thể lập trình cho phạm vi đầu ra 1 hoặc 2 lần

Cơ sở cập nhật đồng thời

Đặt lại bật nguồn bên trong

Tiêu thụ ít điện năng

Nửa bộ đệm

Chi tiết tham khảo datasheet TLV5620

Sơ đồ chân

|

Số chân |

Tên chân |

Mô tả |

|

1 |

GND |

Chân trở lại nối đất và tham chiếu |

|

2 |

REFA |

Đầu vào điện áp tham chiếu cho DAC A. Điện áp này xác định dải analog đầu ra. |

|

3 |

REFB |

Đầu vào điện áp tham chiếu cho DAC B. Điện áp này xác định dải analog đầu ra. |

|

4 |

REFC |

Đầu vào điện áp tham chiếu cho DAC C. Điện áp này xác định dải analog đầu ra. |

|

5 |

REFD |

Đầu vào điện áp tham chiếu cho DAC D. Điện áp này xác định dải analog đầu ra. |

|

6 |

DATA |

Đầu vào dữ liệu kỹ thuật số giao diện nối tiếp. Mã kỹ thuật số cho DAC được ghi tuần tự vào thanh ghi giao diện nối tiếp. Mỗi bit dữ liệu được đồng hồ vào thanh ghi trên cạnh xuống của tín hiệu đồng hồ |

|

7 |

CLK |

Đồng hồ giao diện nối tiếp. Dữ liệu kỹ thuật số đầu vào được chuyển vào thanh ghi giao diện nối tiếp trên cạnh xuống của đồng hồ áp dụng cho chân CLK. |

|

8 |

LOAD |

Kiểm soát tải giao diện nối tiếp. Khi chân LDAC ở mức thấp, cạnh xuống của tín hiệu LOAD sẽ chốt kỹ thuật số dữ liệu vào chốt đầu ra và ngay lập tức tạo ra điện áp analog ở đầu ra DAC. |

|

9 |

DACD |

Đầu ra analog DAC D |

|

10 |

DACC |

Đầu ra analog DAC C |

|

11 |

DACB |

Đầu ra analog DAC B |

|

12 |

DACA |

Đầu ra analog DAC A |

|

13 |

LDAC |

Tải DAC. Khi tín hiệu này ở mức cao, không có cập nhật đầu ra DAC nào xảy ra khi dữ liệu kỹ thuật số đầu vào được đọc vào nối tiếp giao diện. Đầu ra DAC chỉ được cập nhật khi LDAC được chuyển từ cao xuống thấp. |

|

14 |

VDD |

Nguồn dương |

Các ứng dụng

Nguồn điện áp có thể lập trình

Bộ khuếch đại/ Bộ suy giảm điều khiển kỹ thuật số

Truyền thông di động

Thiết bị kiểm tra tự động

Giám sát và kiểm soát quy trình

Tổng hợp tín hiệu