74HC74 là flip flop kiểu D có kích hoạt sườn dương kép. Nó có dữ liệu riêng lẻ (nD), xung nhịp (nCP), đầu vào set (nSD) và reset (nRD) và đầu ra nQ và nQ bổ sung.

Dữ liệu ở đầu vào nD, đáp ứng các yêu cầu về thời gian thiết lập và lưu giữ trong quá trình chuyển đổi đồng hồ THẤP đến CAO, được lưu trữ trong flip flop và xuất hiện ở đầu ra nQ. Hoạt động Schmitt-trigger ở đầu vào xung nhịp, giúp cho mạch có khả năng chịu được thời gian tăng và giảm xung nhịp chậm hơn. Đầu vào bao gồm diode kẹp cho phép sử dụng điện trở hạn chế dòng điện để giao tiếp đầu vào với điện áp vượt quá VCC.

74HC74 giống hệt sơ đồ chân với LS74. Các đầu vào thiết bị là tương thích với các đầu ra CMOS tiêu chuẩn; với điện trở pullup, chúng tương thích với đầu ra LSTTL.

Thiết bị này bao gồm hai flip-flop D với set, reseti riêng lẻ, và đầu vào đồng hồ. Thông tin tại đầu vào D-được chuyển đến đầu ra Q tương ứng trên cạnh dương tiếp theo của đồng hồ đầu vào. Cả hai đầu ra Q và Q đều có sẵn từ mỗi flip flop. Đầu vào set và reset không đồng bộ.

Sơ đồ chân 74HC74

|

Ký hiệu |

Chân |

Mô tả |

|

1RD |

1 |

đầu vào reset trực tiếp không đồng bộ (active LOW) |

|

1D |

2 |

Đầu vào dữ liệu |

|

1CP |

3 |

Đầu vào đồng hồ (thấp đến cao, kích hoạt sườn) |

|

1SD |

4 |

đầu vào set trực tiếp không đồng bộ (active LOW) |

|

1Q |

5 |

Đầu ra |

|

1Q’ |

6 |

Đầu ra bổ sung |

|

GND |

7 |

Ground (0V) |

|

2Q’ |

8 |

Đầu ra bổ sung |

|

2Q |

9 |

Đầu ra |

|

2SD |

10 |

đầu vào set trực tiếp không đồng bộ (active LOW) |

|

2CP |

11 |

Đầu vào đồng hồ (thấp đến cao, kích hoạt sườn) |

|

2D |

12 |

Đầu vào dữ liệu |

|

2RD |

13 |

đầu vào reset trực tiếp không đồng bộ (active LOW) |

|

Vcc |

14 |

Nguồn |

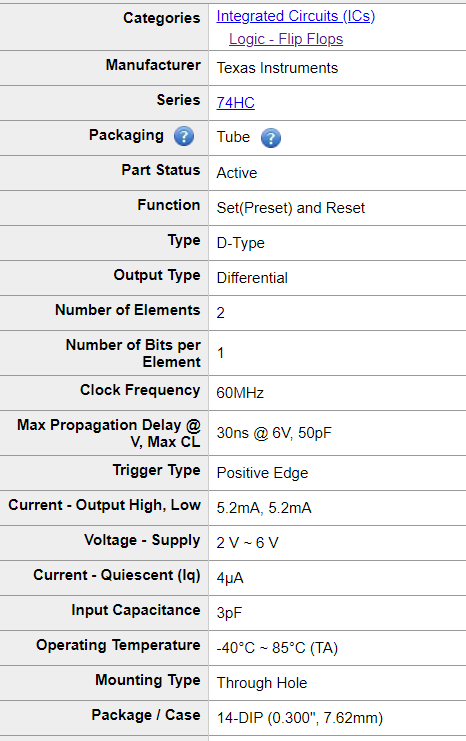

Đặc tính 74HC74

Dải điện áp nguồn rộng từ 2.0 đến 6.0 V

- CMOS tiêu tán năng lượng thấp

- Khả năng chống ồn cao

- Mức đầu vào:

- Đối với 74HC74: cấp CMOS

- Đối với 74HCT74: mức TTL

- Trở kháng đầu ra đối xứng

- Khả năng chống ồn cao

- Sự chậm trễ lan truyền cân bằng

- Hiệu suất theo dõi vượt quá 100 mA trên mỗi JESD 78 Loại II Cấp B

- Tuân theo tiêu chuẩn JEDEC:

- JESD8C (2,7 V đến 3,6 V)

- JESD7A (2.0 V đến 6.0 V)

- Bảo vệ ESD:

- HBM JESD22-A114F vượt quá 2000 V

- MM JESD22-A115-A vượt quá 200 V

- Nhiều tùy chọn gói

- Được chỉ định từ -40 ° C đến +85 ° C và từ -40 ° C đến +125 ° C