74HC192 tương ứng là bộ đếm đồng bộ BCD thập phân và nhị phân Lên / Xuống không đồng bộ được cài đặt trước. Việc đặt trước bộ đếm đến số trên đầu vào dữ liệu đặt trước (P0-P3) được thực hiện bằng đầu vào tải song song không đồng bộ mức thấp (PL). Bộ đếm được tăng lên khi chuyển đổi từ thấp đến cao của đầu vào Clock-Up (và mức cao ở đầu vào Clock-Down) và giảm khi chuyển đổi từ thấp đến cao của đầu vào Clock-Down (và mức cao trên đầu vào Clock-up).

Mức cao trên đầu vào MR sẽ ghi đè bất kỳ đầu vào nào khác để xóa bộ đếm về trạng thái 0 của nó. Terminal đếm lên (carry) xuống thấp trong nửa chu kỳ đồng hồ trước khi đạt đến số không và trở lại mức cao ở số không. Tương tự như vậy, Terminal đến xuống (borrow) ở chế độ đếm ngược sẽ xuống thấp trong nửa chu kỳ đồng hồ trước khi đếm tối đa (9 trong 192) và trở lại cao ở số đếm tối đa. Việc phân tầng được thực hiện bằng cách kết nối các đầu ra carry và borrow của một bộ đếm ít quan trọng hơn với các đầu vào Clock-Up và CLock-Down, tương ứng, của bộ đếm quan trọng nhất tiếp theo.

Đặc tính 74HC192

Đếm đồng bộ và tải không đồng bộ

Hai đầu ra cho N-Bit Cascading

Carry nhìn trước để đếm tốc độ cao

Fanout (Phạm vi nhiệt độ quá cao)

Đầu ra tiêu chuẩn 10 tải LSTTL

Đầu ra trình điều khiển bus 15 tải LSTTL

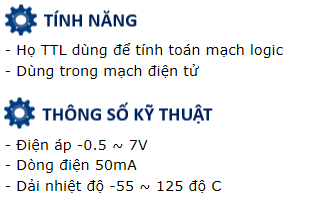

Phạm vi nhiệt độ hoạt động rộng –55 ° C đến 125 ° C

Thời gian chuyển đổi và độ trễ lan truyền cân bằng

Giảm công suất đáng kể so với IC logic LSTTL

Các loại HC

Hoạt động 2V đến 6V

Khả năng miễn nhiễm tiếng ồn cao: NIL = 30%, NIH = 30% VCC tại VCC = 5V

Các loại HCT

Hoạt động 4,5V đến 5,5V

Tương thích logic đầu vào LSTTL trực tiếp, VIL = 0.8V (Max), VIH = 2V (Min)

Tương thích đầu vào CMOS, Il 1µA ở VOL, VOH

Thông số kỹ thuật 74HC192

Đặc điểm kỹ thuật tham số

Họ HC

VCC (Tối thiểu) (V) 2

VCC (Tối đa) (V) 6

Bits (#) 4

Điện áp (Nom) (V) 3,3, 5

Điện áp F @ nom (Tối đa) (MHz) 28

ICC @ nom điện áp (Tối đa) (mA) 0,08

tpd @ nom Điện áp (Tối đa) (ns) 46

IOL (Tối đa) (mA) 5,2

IOH (Tối đa) (mA) -5,2

Bộ đếm chức năng

Nhập thập phân

Nhiệt độ hoạt động © -55 đến 125

Nhóm gói PDIP | 16